User's Guide to

# Accolade PeakVHDL

# **Professional Edition**

550 Kirkland Way, Suite 200 Kirkland, WA 98033 (800) 470-2686 http://www.peakvhdl.com email: sales@peakvhdl.com, support@peakvhdl.com

#### Product License, Limited Warranty and Limitation of Liability (The Small Print)

This software is licensed to you for use by only one person at a time. You may copy the software for archival purposes, but may not distribute the software to persons who are not licensed users of the product. This software is protected by U.S. and international copyright law and cannot be copied or otherwise made available to more one person at a time without violating the law. Giving or otherwise transferring all of your rights to the software to someone else will not violate copyright laws, if you give all of the software and documentation (including this license) to that person. In the event that this software is transferred to another person, you must inform Accolade Design Automation of such a transfer so that the new owner can be registered as an authorized user. Remember, once you transfer your rights to this software to another person, you cannot continue to use the software or keep any copies of the software.

#### Adding More Users

To allow more than one person to use this software, you must purchase additional software for each person.

#### Upgrades

If this software is an upgrade version of software that you previously acquired, you have not acquired two different licenses to use this software and its earlier version. This upgrade and the earlier version together constitute just one copy of the software and must be used by one person (or transferred together to only one person).

#### Other Limits on Your Use

Except as described in this license, you may not transfer, rent, lease, lend, copy, modify, translate, sublicense, timeshare, electronically transmit or receive, or decompile or reverse engineer this software or the media and documentation.

#### **Limited Warranty**

This software package may or may not include a written guarantee, provided by Accolade Design Automation, Inc. or an independent software distributor, which for a limited period of time may entitle you to a full or partial refund of the amount actually paid for the software. Such a guarantee is subject to the terms and conditions described separately, and is not provided (expressly or implicitly) by this license.

Also, the physical media for this software product provided by Accolade Design Automation, Inc. are guaranteed to be free of defects in materials and workmanship for 120 days from the date this product was originally purchased. If a defect occurs within this 120-day period, simply return the defective media to Accolade Design Automation, Inc. and Accolade Design Automation, Inc. will replace it free of charge.

Accolade Design Automation, Inc. makes no representation or warranty regarding the content of this product, including its software and documentation. For example, Accolade Design Automation, Inc. does not warrant that the software and documentation are "error-free" or will meet the needs and requirements of a particular user. All information in the software and documentation is subject to change without notice. In addition, Accolade Design Automation, Inc. makes no representation or warranty regarding products, media, software or documentation manufactured or supplied by others.

ALL OTHER WARRANTIES, REPRESENTATIONS, CONDITIONS, EXPRESS OR IMPLIED, INCLUDING ANY IMPLIED WARRANTY OR CONDITION OF MERCHANTIBILITY OR FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED BY ACCOLADE DESIGN AUTOMATION, INC. ALL OTHER IMPLIED TERMS ARE EXCLUDED.

#### Limitation of Liability

The only remedy under this limited warranty or by any additional guarantee is replacement of the defective media or refund of the actual amount paid. Accolade Design Automation, Inc. disclaims any liability for damages arising from the use of this product or any other damages, including (though not limited to) lost profits or data, special, inciden-

tal, or other claims, even if Accolade Design Automation, Inc. has been specifically advised of the possibility of such claims. Regardless of the form of the claim, the only liability Accolade Design Automation, Inc. will have to you or any other person will be limited to the amount actually paid for the product.

#### Miscellaneous

This license and limited warranty can only be modified in writing signed by you and an authorized officer of Accolade Design Automation, Inc. If any part or provision is found to be unenforceable or void, the remainder shall be valid and enforceable. If any remedy provided is determined to have failed of its essential purpose, all limitations of liability and exclusions of damages shall remain in effect.

Use, duplication or disclosure of this software and documentation by the U.S. Government is subject to the restricted rights applicable to commercial software (under FAR 52.227-19 and DFARS 252.227-7013). Sale of this software is subject to the U.S. Commerce Department export restrictions. This software is intended for use in the country in which it is sold (or the EEC if first sold in the EEC).

This license and limited warranty shall be construed under the laws of the state of Washington, U.S.A.

You have specific legal rights under this document, and may have other rights that vary from state to state, and from country to country.

**COPYRIGHT 1996-1998, Accolade Design Automation, Inc.** All rights reserved. Accolade and Accolade PeakVHDL are trademarks of Accolade Design Automation, Inc. Other brand and product names are trademarks or registered trademarks of their respective holders. Portions of this product are licensed from Green Mountain Computing Systems and are copyright 1995, Green Mountain Computing Systems. All rights reserved.

Third Edition

Printed in the U.S.A.

U0597

# Acknowledgments and Copyrights

The PeakVHDL product and its accompanying documentation have been produced by Accolade Design Automation, Inc. Accolade Design Automation is the holder of copyright to this work, and unauthorized duplication or use of the PeakVHDL product or its documentation, including this manual, are prohibited without the written permission of Accolade Design Automation, Inc. Portions of the PeakVHDL product have been supplied under license by Green Mountain Computing Systems and are copyright 1995-1998, Green Mountain Computing systems.

The information in this manual is subject to change without notice and does not represent any commitment on the part of Accolade Design Automation.

PeakVHDL, PeakFPGA, PeakEDIT, SV/OLE and Accolade VHDL are trademarks of Accolade Design Automation, Inc. Windows is a trademark of Microsoft Corporation. IBM and PC are registered trademarks of International Business Machines Corporation.

Copyright 1995-1996, 1997, 1998, Accolade Design Automation, Inc. All rights reserved.

# Contents

| Acknowledgments and Copyrights             | iv |

|--------------------------------------------|----|

| Chapter 1: What is PeakVHDL?               | 1  |

| Design Management Features                 |    |

| Simulation Features                        |    |

| Synthesis Features                         |    |

| Personal Edition Feature Summary           |    |

| Professional Edition Feature Summary       |    |

| Chapter 2: Installing the Software         | 9  |

| System Requirements                        |    |

| Installing Your Software                   |    |

| Registering Your Software                  |    |

| Chapter 3: Creating a Project              | 15 |

| Creating a New Project                     |    |

| Setting Project Options                    |    |

| Creating a VHDL Module                     |    |

| Adding an Existing VHDL Module             |    |

| Examining the Project Hierarchy            |    |

| Changing the Display Order of VHDL Modules |    |

|                                            |    |

#### Contents

| Summary                                      | 24   |

|----------------------------------------------|------|

| Chapter 4: Using the VHDL Wizard             | . 25 |

| Invoking the New Module Wizard               |      |

| Specifying the Port List                     |      |

| Adding Functionality to Your New Module      |      |

| Compiling the New Module                     | 32   |

| Updating (Rebuilding) Your Project Hierarchy |      |

| Using the Test Bench Wizard                  |      |

| Invoking the Test Bench Wizard               |      |

| Verifying the Port List                      |      |

| Modifying the Test Bench                     |      |

| Summary                                      |      |

|                                              |      |

| Chapter 5: Using Simulation                  | . 41 |

| Understanding Simulation                     | 41   |

| Loading the Sample Project                   | 42   |

| Using the Hierarchy Browser                  | 43   |

| Compiling Modules for Simulation             | 44   |

| Linking Modules for Simulation               |      |

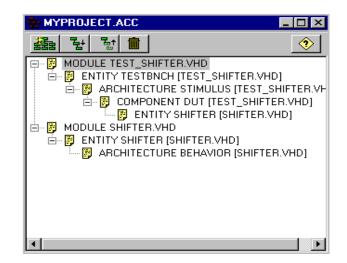

| Setting Simulation Options                   | 49   |

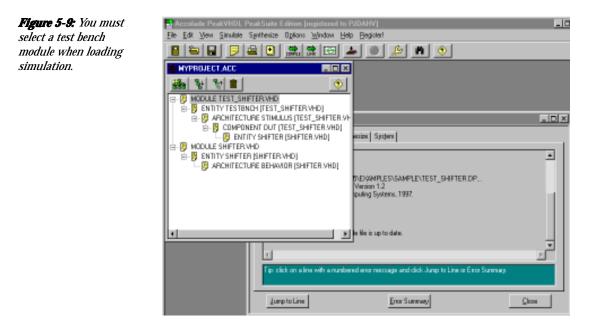

| Loading the Simulation Executable            |      |

| Selecting Signals to Display                 |      |

| Changing Simulation Options                  | 53   |

| Starting a Simulation Run                    |      |

| Summary                                      |      |

| Chapter 6: Using the Debug Window            | . 57 |

| Understanding Source-Level Debugging         |      |

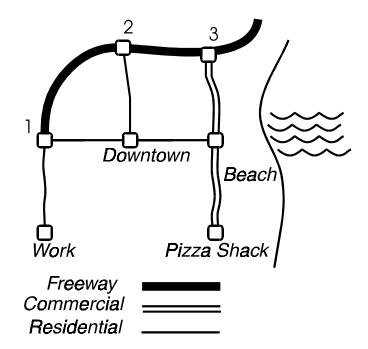

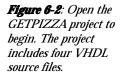

| A Sample Project                             |      |

| Loading the Sample Project                   |      |

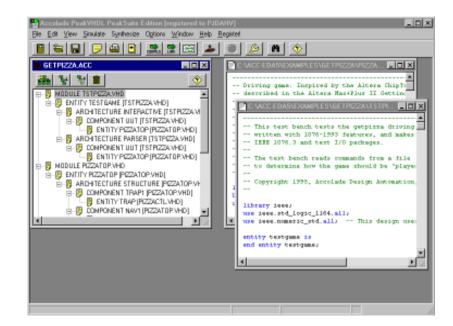

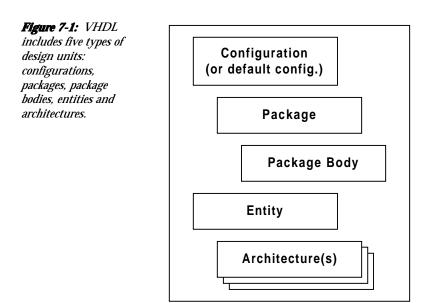

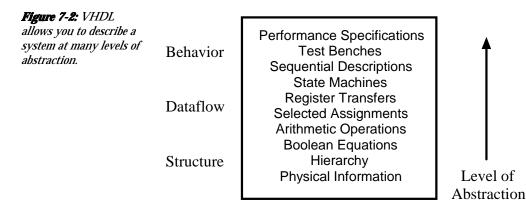

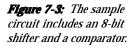

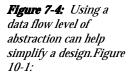

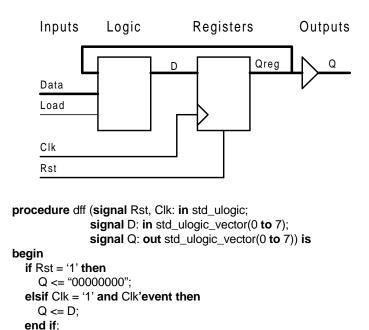

| Loading the Simulation62Setting a Break Point64Running Simulation64Summary66Chapter 7: A First Look at VHDL67What Is VHDL?67A Brief History Of VHDL69Learning VHDL73Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105PeakLIB Overview105 | Setting Project Options         |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|

| Setting a Break Point64Running Simulation64Summary66Chapter 7: A First Look at VHDL67What Is VHDL?67A Brief History Of VHDL69Learning VHDL73Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)98Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                          |                                 |     |

| Running Simulation64Summary66Chapter 7: A First Look at VHDL67What Is VHDL?67A Brief History Of VHDL69Learning VHDL73Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                 |                                 |     |

| Summary66Chapter 7: A First Look at VHDL67What Is VHDL?67A Brief History Of VHDL69Learning VHDL73Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                     | 8                               |     |

| Chapter 7: A First Look at VHDL67What Is VHDL?67A Brief History Of VHDL69Learning VHDL73Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103                                                                                                         |                                 |     |

| What Is VHDL?67A Brief History Of VHDL69Learning VHDL73Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                               | 5                               |     |

| What Is VHDL?67A Brief History Of VHDL69Learning VHDL73Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                               | Chapter 7: A First Look at VHDL | 67  |

| A Brief History Of VHDL69Learning VHDL73Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                                              | -                               |     |

| Learning VHDL73Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                                                                       | A Brief History Of VHDL         |     |

| Entities and Architectures74Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                                                                                      | Learning VHDL                   |     |

| Entity Declaration75Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                                                                                                                  |                                 |     |

| Architecture Declaration76Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103                                                                                                                                                                                                                                                 |                                 |     |

| Data Types77Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB                                                                                                                                                                                                                                                   | -                               |     |

| Design Units78Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB                                                                                                                                                                                                                                                               |                                 |     |

| Levels of Abstraction (Styles)81Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB                                                                                                                                                                                                                                                                             |                                 |     |

| Sample Circuit84Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB                                                                                                                                                                                                                                                                                                             |                                 |     |

| Comparator (Dataflow)86Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB                                                                                                                                                                                                                                                                                                                             |                                 |     |

| Barrel Shifter (Entity)89Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                                                                                                                                                                                                                                                                 |                                 |     |

| Signals and Variables94Using a Procedure95Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                                                                                                                                                                                                                                                                                          |                                 |     |

| Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                                                                                                                                                                                                                                                                                                                                    |                                 |     |

| Structural VHDL98Design Hierarchy98Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                                                                                                                                                                                                                                                                                                                                    | Using a Procedure               |     |

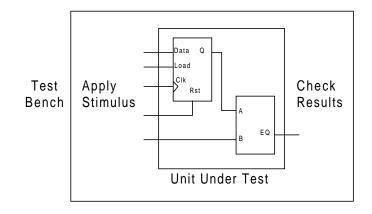

| Test Benches100Sample Test Bench102Conclusion103Chapter 8: Using PeakLIB105                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                 |     |

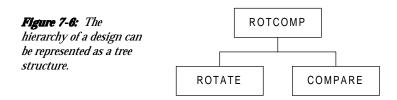

| Sample Test Bench    102      Conclusion    103      Chapter 8: Using PeakLIB    105                                                                                                                                                                                                                                                                                                                                                                                                                                              | Design Hierarchy                |     |

| Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Test Benches                    |     |

| Chapter 8: Using PeakLIB 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Sample Test Bench               |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Conclusion                      | 103 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chapter 8: Using PeakLIB        |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |     |

| Examining the Contents of a Library File                                                                                                                                                                                                                                                                  | 106                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Adding a .AN File to a Library                                                                                                                                                                                                                                                                            | 106                                                                                            |

| Deleting a .AN File Reference From a Library                                                                                                                                                                                                                                                              | 107                                                                                            |

| Appendix A: Support Services                                                                                                                                                                                                                                                                              | 109                                                                                            |

| Learning More About VHDL                                                                                                                                                                                                                                                                                  |                                                                                                |

| Obtaining Product Assistance                                                                                                                                                                                                                                                                              |                                                                                                |

| Reporting Bugs                                                                                                                                                                                                                                                                                            | 110                                                                                            |

| Appendix B: Glossary                                                                                                                                                                                                                                                                                      | 113                                                                                            |

| Appendix C: Examples Gallery                                                                                                                                                                                                                                                                              |                                                                                                |

| Using Type Conversion Functions                                                                                                                                                                                                                                                                           | 128                                                                                            |

| Using Components                                                                                                                                                                                                                                                                                          | 132                                                                                            |

| Using Generate Statements                                                                                                                                                                                                                                                                                 |                                                                                                |

| Understanding Sequential Signal Assignments                                                                                                                                                                                                                                                               | 139                                                                                            |

| Describing A State Machine                                                                                                                                                                                                                                                                                | 144                                                                                            |

|                                                                                                                                                                                                                                                                                                           |                                                                                                |

| Reading And Writing From Files                                                                                                                                                                                                                                                                            |                                                                                                |

| Reading And Writing From Files                                                                                                                                                                                                                                                                            | 150                                                                                            |

| Reading And Writing From Files Appendix D: SV/OLE Reference                                                                                                                                                                                                                                               | 150<br><b>157</b>                                                                              |

| Reading And Writing From Files<br>Appendix D: SV/OLE Reference<br>SV/OLE Operation Overview                                                                                                                                                                                                               | 150<br><b>157</b><br>158                                                                       |

| Reading And Writing From Files Appendix D: SV/OLE Reference                                                                                                                                                                                                                                               | 150<br><b>157</b><br>158<br>160                                                                |

| Reading And Writing From Files<br>Appendix D: SV/OLE Reference<br>SV/OLE Operation Overview<br>FUNCTION SVOLE.Args()<br>FUNCTION SVOLE.AtomToName()                                                                                                                                                       | 150<br>157<br>158<br>160<br>161                                                                |

| Reading And Writing From Files<br>Appendix D: SV/OLE Reference<br>SV/OLE Operation Overview<br>FUNCTION SVOLE.Args()                                                                                                                                                                                      |                                                                                                |

| Reading And Writing From Files<br>Appendix D: SV/OLE Reference<br>SV/OLE Operation Overview<br>FUNCTION SVOLE.Args()<br>FUNCTION SVOLE.AtomToName()<br>FUNCTION SVOLE.CurrentBP()<br>FUNCTION SVOLE.DeleteBP()                                                                                            |                                                                                                |

| Reading And Writing From Files<br>Appendix D: SV/OLE Reference<br>SV/OLE Operation Overview<br>FUNCTION SVOLE.Args()<br>FUNCTION SVOLE.AtomToName()<br>FUNCTION SVOLE.CurrentBP()<br>FUNCTION SVOLE.DeleteBP()<br>FUNCTION SVOLE.DeleteBP()                                                               |                                                                                                |

| Reading And Writing From Files<br><b>Appendix D: SV/OLE Reference</b><br>SV/OLE Operation Overview<br>FUNCTION SVOLE.Args()<br>FUNCTION SVOLE.AtomToName()<br>FUNCTION SVOLE.CurrentBP()<br>FUNCTION SVOLE.DeleteBP()<br>FUNCTION SVOLE.DeleteBP()<br>FUNCTION SVOLE.DeltaStep()<br>FUNCTION SVOLE.Exit() |                                                                                                |

| Reading And Writing From Files<br>Appendix D: SV/OLE Reference                                                                                                                                                                                                                                            |                                                                                                |

| Reading And Writing From Files<br><b>Appendix D: SV/OLE Reference</b><br>SV/OLE Operation Overview<br>FUNCTION SVOLE.Args()<br>FUNCTION SVOLE.AtomToName()<br>FUNCTION SVOLE.CurrentBP()<br>FUNCTION SVOLE.DeleteBP()<br>FUNCTION SVOLE.DeleteBP()<br>FUNCTION SVOLE.DeltaStep()<br>FUNCTION SVOLE.Exit() |                                                                                                |

| Reading And Writing From Files                                                                                                                                                                                                                                                                            |                                                                                                |

| Reading And Writing From Files<br>Appendix D: SV/OLE Reference                                                                                                                                                                                                                                            | 150<br>157<br>158<br>160<br>161<br>162<br>163<br>164<br>165<br>166<br>167<br>167<br>168        |

| Reading And Writing From Files                                                                                                                                                                                                                                                                            | 150<br>157<br>158<br>160<br>161<br>162<br>163<br>164<br>165<br>166<br>167<br>167<br>168<br>169 |

| FUNCTION SVOLE.GetVariables()                   |     |

|-------------------------------------------------|-----|

| FUNCTION SVOLE.GetVarType()                     | 174 |

| FUNCTION SVOLE.NameToAtom()                     | 175 |

| FUNCTION SVOLE.QueryDone()                      | 176 |

| FUNCTION SVOLE.QueryPercentDone()               | 177 |

| FUNCTION SVOLE.QueryStatus()                    | 177 |

| FUNCTION SVOLE.Reset()                          | 179 |

| FUNCTION SVOLE.Run()                            | 180 |

| FUNCTION SVOLE.RunForever()                     | 180 |

| FUNCTION SVOLE.SetBP()                          | 181 |

| FUNCTION SVOLE.SetInput()                       | 182 |

| FUNCTION SVOLE.SingleStep()                     | 183 |

| FUNCTION SVOLE.Start()                          | 185 |

| FUNCTION SVOLE.Stop()                           | 185 |

| FUNCTION SVOLE.TimeNow()                        |     |

| PROPERTY SVOLE. TimeStep                        | 187 |

| PROPERTY SVOLE. TimeUnits                       | 188 |

| Simulation History (SimHist) Interface          | 189 |

| FUNCTION SimHist.AddWatch()                     | 190 |

| FUNCTION SimHist.ClearAll()                     | 191 |

| FUNCTION SimHist.ClearEvents()                  | 192 |

| FUNCTION SimHist.DeleteEvents()                 | 193 |

| FUNCTION SimHist.DeleteWatch()                  | 194 |

| FUNCTION SimHist.GetEvents()                    | 195 |

| FUNCTION SimHist.GetValueAt()                   | 196 |

| FUNCTION SimHist.GetWatches()                   | 197 |

| FUNCTION SimHist.TimeNow()                      | 198 |

| PROPERTY SimHist.TimeUnits                      | 199 |

| Event Iterator (EventIterator).                 | 200 |

| FUNCTION EventIterator.Current()                |     |

| FUNCTION EventIterator.First()                  | 201 |

| FUNCTION EventIterator.GetAsString()            | 202 |

| FUNCTION EventIterator.IsEmpty()                | 205 |

| FUNCTION EventIterator.IsFirst() return Boolean | 205 |

| FUNCTION EventIterator.IsLast()                 | 206 |

|                                                 |     |

| FUNCTION EventIterator.Last()<br>FUNCTION EventIterator.Next() |     |

|----------------------------------------------------------------|-----|

| FUNCTION EventIterator.Previous()                              |     |

| FUNCTION EventIterator.Reset()                                 | 209 |

| Event Object (Event)                                           | 210 |

| FUNCTION Event.Time()                                          |     |

| FUNCTION Event.Value()                                         | 211 |

| Index                                                          |     |

# Chapter 1: What is PeakVHDL?

PeakVHDL<sup>™</sup> is a design entry and simulation system that is intended to help you learn and use the VHDL language for advanced circuit design projects. The system includes a VHDL simulator, source code editor, hierarchy browser and on-line resources for VHDL users. If you have purchased a synthesis option, PeakVHDL allows you to control synthesis options and start the synthesis process from right within the PeakVHDL environment.

You can use PeakVHDL to create and manage new or existing VHDL projects. Because VHDL is a standard language, you can use PeakVHDL in combination with other tools (including schematic editors, high-level design tools, and other tools available from third parties) to form a complete electronic design environment.

## **Design Management Features**

PeakVHDL includes many useful features that help you to create, modify and process your VHDL projects. The Hierarchy Browser, for example, shows you an up-to-date view of the structure of your design as you are entering it. This is particularly useful for projects that involve multiple VHDL source files (called *modules*) and/or multiple levels of hierarchy.

The VHDL Wizards helps you create new VHDL design descriptions, by asking you a series of questions about your design requirements, and generating VHDL source file templates for you based on those requirements.

The built-in dependency ('make') features help you streamline the processing of your design for simulation and for synthesis. When you are ready to simulate your design, for example, you simply highlight the design unit (whether a source file module, entity, architecture, etc.) you wish to have processed and click a single button. There is no need to compile each VHDL source file in the design, or to keep track of your source file dependencies. PeakVHDL does it for you.

# **Simulation Features**

PeakVHDL's built-in simulator is a complete system for the compilation and execution of VHDL design descriptions. The simulator includes a VHDL analyzer (compiler), elaborator, code generator and simulation kernel. VHDL design descriptions are compiled into a 32-bit native Windows executable form. When run, these executable files interact with the PeakVHDL system to allow interactive debugging of your circuit.

The PeakVHDL analyzer, elaborator, code generator and simulation kernel are native 32-bit Windows applications; meaning that they are fast and capable of processing very large design descriptions.

Simulation results (in the form of graphical waveforms and/ or textual output) can be easily saved for use in other tools, or printed on any Windows-compatible printer.

# **Synthesis Features**

PeakVHDL's optional synthesis packages allow design descriptions to be quickly and easily processed into netlists optimized for specific target hardware, such as FPGA devices. Synthesis options are controlled from within PeakVHDL's Options dialog box. The PeakVHDL Hierarchy Browser is used to invoke synthesis, allowing complete control over the synthesis process.

# Personal Edition Feature Summary

The following features have been provided in PeakVHDL Personal Edition, and are also available in more advanced versions of PeakVHDL:

#### **Hierarchy Browser**

The Hierarchy Browser provides you with one centralized place to control the processing of your design, invoke the built-in editor to modify your design, and see how the various modules of your design are related. In addition, the Hierarchy Browser acts as a dependency checking feature, ensuring that the files associated with your project are processed in the correct order and kept up-to-date as you make modifications to them.

#### **Source File Editor**

The built-in editor allows you to quickly create and edit VHDL source files and other ASCII text files associated with your project. The editor includes useful features such as syntax coloring, automatic indenting, and global (multi-file) search capabilities.

#### **VHDL Wizards**

The VHDL Wizards help you to quickly create new VHDL modules and add them to your project. The Wizards allow you to enter the top-level specification of a design module (in the form of a port list) and automatically generates a VHDL source file template and template test bench.

#### **VHDL Compiler and Linker**

The PeakVHDL is a native-compile simulator that processes (compiles) VHDL design descriptions into Windows-compatible native x86 bject code. The VHDL compiler included with PeakVHDL Personal Edition provies support for most features of the VHDL language. (Limitations are described on the Accolade Design Automation Web site.)

The object code generated by the compiler is linked automatically to create a simulation executable compatible with PeakVHDL's SVOLE execution kernel. The PeakSIM simulation interface (see below) provides you with a graphical view of simulation results and allows you to select signals and control simulation execution.

#### **PeakSIM Waveform Interface**

The PeakSIM waveform display provides you with a graphical representation of your simulation results in a format similar to a logic analyzer. VHDL data types (including user-defined types) are dispayed in an easy-to-view format, and the interface allows you to select and order signals in the display at any time during simulation. Selectable measurement cursors make it easy to compare and measure waveform events, and a transcript window makes it easy to observe messages (such as text I/O) generated from your design as it executes.

#### Sample Projects

PeakVHDL Personal Edition includes dozens of sample VHDL projects to help you come up-to-speed quickly with the language and its important concepts. These projects may be copied and modified as needed as you develop your own VHDL-based projects.

## **Professional Edition Feature Summary**

The following features have been provided in PeakVHDL Professional Edition, in addition to those features provided in PeakVHDL Personal Edition:

#### High-performance VHDL Analyzer and Elaborator

The Professional Edition simulator includes advanced VHDL compiler technology with faster performance and greater design capacities than are available in the Personal Edition product. The Professional Edition x86 code generator is optimized for today's high-performance x86-based processors.

#### **Debugging Window**

The source-level debugging window allows you to follow the execution of your VHDL design at the level of VHDL source file statements. This is particularly useful for debugging complex sequential statements, determining the order in which statements are processed, and understanding the impact of scheduling, delta cycles and other complex aspects of model execution.

#### **Break Points**

An important feature of the source level debugging window is the ability to set break points in your VHDL code. Break points are points at which the simulation will pause execution, making it easier for you to step through the code to analyze its execution and find errors.

#### VITAL (IEEE 1076.4) Support

When purchased with the PRO+VITAL option, the Professional Edition simulator product supports timing annotation using VITAL (IEEE 1076.4) compliant netlists and SDF timing data files. This feature is important for performing post-route timing simulation of FPGAs and other devices.

#### **Command Window**

The command window allows you to enter text commands, or control the execution of command files, from within the PeakSIM simulation interface. The commands available in this window give you more complete control over the simulation process, including the ability to force individual signals to specific values during debugging.

## **SV/OLE Programming Interface**

The SV/OLE programming interface makes it possible for you to run your compiled and linked PeakVHDL projects as standalone Windows applications, and to interface the resulting simulation executable files directly to OLE-enabled programming environments such Visual Basic and Visual C++. This feature gives you tremendous power by allowing a form of hardware/software co-simulation. To help you get started with this powerful feature, a comprehensive on-line SV/OLE reference guide and a sample Visual Basic application are included with your PeakVHDL Professional Edition installation.

#### PeakLIB

The PeakLIB program supplied with PeakVHDL Professional Edition can be used to create and maintain PeakVHDL library files from your previously-compiled VHDL object files. PeakLIB is a DOS application, and is described in detail later in this manual.

#### **PeakFPGA Integration**

PeakVHDL Professional Edition is designed to integrate tightly with PeakFPGA<sup>™</sup> for the best in FPGA synthesis. PeakFPGA is a full featured FPGA Synthesis tool that supports all major FPGA device families.

# **Chapter 2: Installing the Software**

The PeakVHDL software follows established Windows software installation methods. The instructions in this chapter assume you will be installing the software from CD-ROM. The installation procedure for diskette distribution is similar, and is not described here.

After installing the software, but before making full use of it, you will need to register the software using a valid serial number and permanent authorization code. Follow the instructions in this chapter carefully to make sure you have correctly installed and registered the software.

#### System Requirements

The PeakVHDL software will install and run on any Microsoft Windows based personal computer meeting the following criteria:

- Windows 95/98 or Windows NT operating system.

- Intel (or equivalent) 486 or Pentium processor.

- 16MB (or greater) RAM.

- 17MB of available disk space (65MB with all libraries and options).

## **Installing Your Software**

The PeakVHDL software is supplied on CD-ROM. Installation of the software is simple, and follows standard Windows installation methods.

Begin the installation by inserting the distribution CD-ROM into your CD-ROM drive unit. From My Computer or Explorer, invoke the setup utility (SETUP.EXE) found on the distribution CD-ROM.

*Note: When installing, do not choose a directory that includes spaces in the path. An example of this is C:\Program Files\.*

#### **Selecting Product Options**

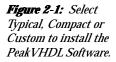

When you begin installation, the installation software will prompt you for an installation directory and allow you to select the product features you wish to install (Figure 2-1). Choose Typical to install all files (including synthesis options) to your hard disk, or choose Compact to install only the minimum files needed for simulation. Choose Custom to remove certain product features (such as on-line manuals) from the installation if disk space is at a premium.

After installing the software on your hard disk drive, the program will create (or update) the appropriate entires in your Windows Registry, and will create a Start menu program group and items as appropriate. You then have the option to invoke PeakVHDL immediately, or you can exit the install routines and run PeakVHDL at a later time.

Note:

The PeakVHDL software does not require any modifications to your system files (such as AUTOEXEC.BAT or CONFIG.SYS).

# **Registering Your Software**

Before beginning with PeakVHDL, you should take a moment to register the product. Although the product can be used with the Temporary Authorization Code (which has been provided for you with the software distribution), this Temporary Authorization Code will expire in as few as thirty days after you receive the software.

#### 1. Determine Your Node ID

Before registering your software, you will need to determine the Node ID of your computer system. To determine the Node ID of your system, invoke the Display Node ID application that was installed with PeakVHDL in the **Programs / PeakVHDL** section of the Windows **Start** menu.

The Node ID is generated for your system based on certain hardware and software characteristics. There are some system upgrade or replacement situations in which your Node ID will change. If this occurs, simply contact Accolade Design Automation product support to obtain a new authorization code.

#### 2. Obtain a Permanent Authorization Code

To permanently enable the software, you must obtain a Permanent Authorization Code from Accolade Design Automation, using the automated registration system found at the following URL: **http://www.acc-eda.com**.

#### Note:

If you do not have access to the World Wide Web, or are having problems accessing the automated registration system, you can obtain your authorization code direct from Accolade Design Automation. Refer to your printed distribution materials for the appropriate FAX or voice phone number. Site License users must contact Accolade Design Automation directly for a Site License Authorization Code.

When registering your software with the automated registration system, be sure to enter your name and serial number(s) correctly and completely. Your Permanent Authorization Code is tied directly to your Node ID (or site license name), and cannot be used by others. Also be sure to complete the user information section, including your complete phone number and address.

#### 3. Enter the Authorization Code in the Software

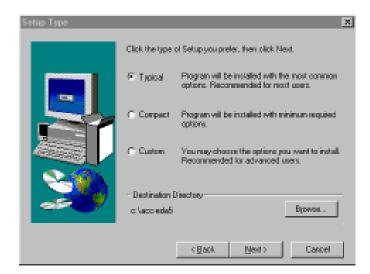

After you have received your Personal Authorization Code, or to use temporary Authorization Code, enter the information into the Options dialog box, in the Registration tag as shown in Figure 2-2.

(You access the registration dialog by selecting the Register item from the PeakVHDL main application window.)

Enter your name, product Serial Number(s) and Personal Authorization Code in the appropriate fields. Check to make sure they are entered correctly. If you have purchased multiple product options (such as PeakVHDL simulation and PeakFPGA synthesis), enter all associated serial numbers in the Serial Number(s) field, using commas between the serial numbers as shown. **Click on the Click Here to Register** button to verify the authorization code and enable the product, then click the **OK** button to exit the registration dialog.

Your PeakVHDL software is now ready for use.

| Registration Information     Serial numbers (required)         | · Autholization code (required)                                                                                                                                                            |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC/1100339. ADCFPG50339                                       | 132999                                                                                                                                                                                     |

| Node ID or Site License name                                   | C Register using Site Licence nerve                                                                                                                                                        |

| PIDAHV                                                         | Register using Node ID (node locked license)                                                                                                                                               |

| Dick her                                                       | te to segister your oofware                                                                                                                                                                |

| Authorization Eode before clicking the Register<br>upper case. | g it. Caerfully check the spelling of your Smish Number(s) an<br>Duiton. Please note that Serial Numbers must be entered in<br>In code, you may enter your temporary authorization code an |

|                                                                |                                                                                                                                                                                            |

# Chapter 3: Creating a Project

PeakVHDL operates on one or more VHDL source files that are referenced in a PeakVHDL *project file*. This chapter will describe how to create and use PeakVHDL projects, and how to create or import VHDL source files into a PeakVHDL project.

A PeakVHDL project is composed of a project file and one or more VHDL source files, which are refered to as *modules*. The project file, in addition to containing references to the various VHDL modules in your project, also includes various option settings that you have specified for the project. Each module (VHDL source file) includes one or more VHDL design units that can be selected as needed when the design is processed.

Project files (which are created with a .ACC file name extension when you select **Save Project** from the **File** menu) include information about the VHDL modules used in the design, as well as the project-specific options that you have specified. Project files do not include the actual VHDL source statements for your design; instead, the VHDL source statements are maintained in separate VHDL source files, which normally have .VHD file name extensions.

#### Note

*PeakVHDL allows you to use alternative file name extensions, such as .VHDL or VHO, but the built-in text editor will only recognize files with a .VHD file name extension for the purpose of VHDL syntax coloring.*

#### **Creating a New Project**

This and the following sections will take you step-by-step through the creation of a new PeakVHDL project, beginning with the creation of a blank project. First invoke the PeakVHDL application then, to create a new project:

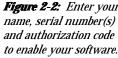

**1.** Select **New Project** from the **File** menu, or click on the New Project icon.

A blank project will be created, and the Hierarchy Browser will appear . The Hierarchy Browser will contain references to each new VHDL module as it is added or created. Before continuing, it is a good idea to establish a working directory and project name by saving the project file. To save the project and give it a name:

**2.** Select **Save Project As** from the **File** menu , or click on the Save Project icon in the PeakVHDL toolbar in Figure 3-1.

After saving your project with a name, you are ready to begin creating or importing VHDL source file modules.

First, however, you may want to set a few project options.

## **Setting Project Options**

PeakVHDL includes a variety of program options that you can specify. Some options available in PeakVHDL (such as compile flags and library paths) are related to specific projects, while others (such as the text editor font and toolbar settings) are more general and system-wide. As you learn and

use PeakVHDL's many features, you will find it useful to customize the options settings for your own preferences, and for the requirements of your projects.

To set PeakVHDL options:

- **1.** Open the Options dialog (Figure 3-2), either by selecting any item from the **Options** menu, or by clicking on the Options icon in the PeakVHDL toolbar.

- **2.** Use the tabbed dialog feature to select the desired option tab.

The Options dialog allows you to set a variety of options related to compilation, linking, simulation, synthesis and general program operation. (The options available to you will depend on the specific product version that you have purchased. For detailed information about available options, please consult the PeakVHDL on-line help information.)

#### Chapter 3: Creating a Project

#### Figure 3-2:

PeakVHDL Options dialog allows you to set a variety of project options related to simulation and synthesis. PeakVHDL also includes system options so you can customize the appearance and features of your PeakVHDL installation.

| Compaile ceder                                                           | - Compile options                                                                                                      | •        |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------|

| C Selected lie only                                                      | 🖓 Compile only if out of date 🛛 🧲                                                                                      | -        |

| Bottomup to selected                                                     | A AHDT 33                                                                                                              |          |

| Options for selected readule                                             |                                                                                                                        |          |

| Selected module manie                                                    | Compile into library External ("\use") libraries                                                                       | ^        |

|                                                                          |                                                                                                                        |          |

|                                                                          |                                                                                                                        | Ŷ        |

|                                                                          |                                                                                                                        | V        |

| p compile options apply only to sig                                      | n Astron completion. If you choose not to use EEE standard 1076-1953                                                   | 3        |

| o, compile options apply only to sa<br>HDL '93), you must also change if | Indefent compilation. If you choose not to use EEE standard 1076-1993<br>a System Likeway Path under the System tab.   | <u>?</u> |

| p: compile options apply only to sk<br>HDL '93), you much also change fi | Adation compilation. If you choose not to use IEEE standard 1076-1993<br>a System Library Plafn under the System tab.  | ?        |

| p. compile options apply only to sa<br>HDL '93), you must also change f  | wation compilation. If you choose not to use IEEE standard 1076-1993<br>a System Library Path under the System tab.    | •        |

| p: compile options apply only to se<br>HDL '93), you must also change f  | wisiton compilation. If you choose not to use IEEE standard 1076-1993<br>a System Library Path under the System tab.   | •        |

| p: compile options apply only to se<br>HDL '93), you must also change f  | wisition compilation. If you choose not to use IEEE standard 1076-1963<br>• System Library Path under the System tab.  | •        |

| or compile options apply only to se<br>HDL '93), you must also change if | wisition compilation. If you choose not to use IEEE standard 1076-1963<br>• System Library Plath under the System tab. | ?        |

Most options that you specify in the Options dialog are saved with your project, so you can tailor the options to the requirements of a specific project. If you wish to save the options specified as the default options for all new projects, you can check the **Save options as default** option before exiting the PeakVHDL application.

When you have finished setting (or simply examining) the Options dialog:

**3.** Click **OK** to exit the dialog and save your new option settings, *or* click Cancel to exit the dialog without saving the new settings.

## **Creating a VHDL Module**

There are two ways to add VHDL modules to your project, depending on whether you are building a project from existing VHDL source files or are creating a new project from scratch. If you do not already have one or more VHDL source files to work with, you will begin by creating a new, blank VHDL module. To create a new VHDL module:

**1.** Select **New Module** from the **File** menu, or click on the New Module icon. The New Module dialog will appear as shown in Figure 3-3.

#### Note

If you have not already saved your new project, you will be prompted to save it before the New Module dialog appears.

| New Module                | ×           |

|---------------------------|-------------|

| Add new module to project | <b>&gt;</b> |

| Module Wizard             |             |

| Test Bench Wizard         |             |

| Create Blank Module       | Cancel      |

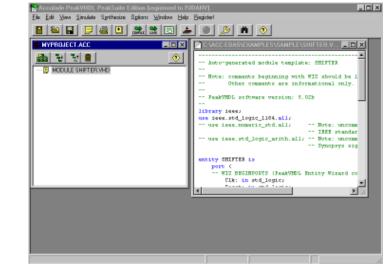

The New Module dialog box has three buttons that allow you to create new modules. The **Module Wizard** and **Test Bench Wizard** buttons invoke the VHDL Wizard, which is described in detail in Chapter 4. The **Create Blank Modul**e button adds a new, empty module to your project.

**2.** Click the **Create Blank Module** button to create a new, empty VHDL module.

#### Note

By default, the New Module dialog will add the new module to your project so it is displayed in the Hierarchy Browser. If you do not wish to have the module added to the Hierarchy Browser, you should deselect the **Add new module to project** field in the New Module dialog.

Figure 3-3: Use the New Module button to create a new VHDL module (source file). You can create an empty module, or invoke the Module Wizard or Test Bench Wizard to create a module or test bench template. At this point, you could add some VHDL source statements to the empty module and save it (using **Save Module As** from the **File** menu). To continue this tutorial, however, you must delete the newly-created VHDL module and go on to the next section.

**3**. Delete the newly-created module by first closing the text editing window, then highlighting the module name in the Hierarchy Browser and selecting **Remove Module** from the **File** menu.

#### Note

Removing a module from the Hierarchy Browser does not remove the file from your hard disk. **Remove Module** only removes the reference to the specified file from the project file.

## Adding an Existing VHDL Module

To import already-existing VHDL source files (created outside of PeakVHDL) into your project, or to copy and use a module (such as a test bench) from one of the PeakVHDL standard examples, use the **Add Module** feature instead of **New Module**. The **Add Module** feature, which is accessed by selecting **Add Module** from the **File** menu, or by clicking the Add Module icon, adds one or more VHDL source file to the Hierarchy Browser display, and to the project. To understand how this works, use the **Add Module** feature to import all the VHDL source file modules from one of the PeakVHDL standard examples:

- **1.** Click the **Add Module** button (or select **Add Module** from the **File** menu).

- **2.** Navigate to the PeakVHDL examples directory (typically "\acc-eda5\examples") and select one of the PeakVHDL example directories (for example, "examples\shifter", as shown in Figure 3-4).

Figure 3-4: To add one or more existing VHDL modules to the project, select the Add Module button. If the module is not in the current project directory, it will be copied.

| Accelade PeakVHDL         | PeakSuite Edition (registered to f | UDAHV]    |        |    |

|---------------------------|------------------------------------|-----------|--------|----|

| Elle Edit View Simulate   | Synthesize Options Window Help     | Begistert |        |    |

|                           | 4 🖸 🌨 🕿 🔺                          |           | ۲      |    |

| WYPROJECT.ACC             |                                    |           |        |    |

| 🏭 😵 🐄 🔳                   | ) 🔬                                |           |        |    |

|                           | Open                               |           | ? ×    |    |

|                           | Look jn: 🔄 cache                   |           |        |    |

|                           | cache.vhd                          |           |        |    |

|                           | totoache, vhd                      |           |        |    |

|                           |                                    |           |        |    |

|                           |                                    |           |        |    |

|                           |                                    |           |        |    |

|                           | File game:                         |           | Quen   |    |

|                           | Files of type: vhd Files (1.vh?)   | ×         | Cancel |    |

|                           |                                    |           | 00100  |    |

|                           |                                    |           |        |    |

|                           |                                    |           |        |    |

|                           |                                    |           |        |    |

|                           |                                    |           |        |    |

| Dane witing project lile. |                                    |           |        | 16 |

- **3.** Highlight (using the shift key and mouse) all .VHD files listed.

- **4.** Click the **Open** button to add all selected .VHD files to your project.

When you import modules using **Add Module**, if the selected VHDL source files are not in the current project directory, they will be copied to the current directory before being added to the project.

#### Note

It is not possible to create projects that directly reference VHDL files located in other directories. You can, however, use the library features of PeakVHDL to create precompiled modules in different directories on your system. Refer to Chapter 8, Using PeakLIB, for more details on PeakVHDL's library features.

# **Examining the Project Hierarchy**

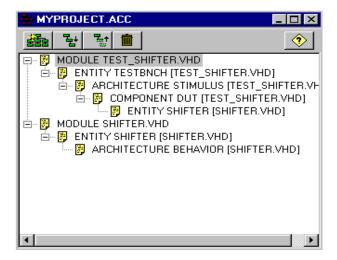

When you have created or imported one or more VHDL modules for your project, you can easily examine the hierarchy of each module and the see the relationships between design units found within those modules. To examine the hierarchy of the project:

- **1.** Make the Hierarchy Browser the active window (by clicking the mouse once within it, or on its title bar).

- **2.** Select **Rebuild Hierarchy** from the **File** menu or use the Rebuild Hierarchy button.

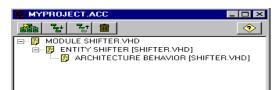

When **Rebuild Hierarchy** is invoked, all modules in the project are analyzed and a hierarchy tree is created. After the tree is created, you will see small "+" icons appearing next to each VHDL module (Figure 3-5). You can use these "+" icons to push into each module and examine its contents, or you can use the **Show Hierarchy** button (shown below) to expand and view the entire project hierarchy:

When you examine the complete hierarchy for a module (either by repeatedly clicking on the "+" icons or by clicking once on the **Show Hierarchy** icon), you will see listed not only the design units that exist in the current module, but those that exist in other modules referenced from the current

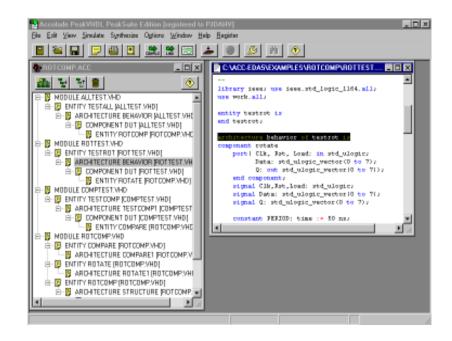

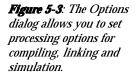

Figure 3-5: Use the Rebuild Hierarchy button to bring the Hierarchy Browser upto-date. You should rebuild the project hierarchy after any change to a module that might impact the project hierarchy.

#### Examining the Project Hierarchy

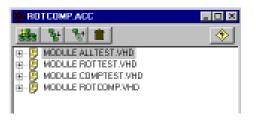

Figure 3-6: After you select the Rebuild Hierarchy feature, the Hierarchy Browser displays the hierarchy for each module in the project. You can invoke the text editor by double-clicking on any entry in the Hierarchy Browser.

module as well. If you wish to examine the VHDL source file associated with any design unit listed in a module's hierarchy tree, you can double-click on the design unit name and the source file will be loaded into PeakVHDL's built-in source file editor. This editor (shown in Figure 3-6) is a full-featured text editor and includes features such as search and replace, keyword coloring, and drag-and-drop editing features.

#### Note

# If you prefer to use your own text editor, you can specify an alternate source file editor in the System Options dialog box.

Although you can edit and compile VHDL modules without first rebuilding the project hierarchy, you will not be able to link or load a module for simulation, or invoke synthesis or optimization without first bringing the project hierarchy upto-date. In addition, you should keep in mind that the project hierarchy is not updated automatically as you modify your project. You should therefore be sure to rebuild the hierarchy any time you make a change to the project that might impact the hierarchy of the project. Changes that can impact the hierarchy include:

- Adding or removing VHDL modules

- Changing compile library names

- Adding or removing component references

- Changing entity, architecture or component names

- Modifying references to external packages

#### Changing the Display Order of VHDL Modules

As you add new modules to your project, you may wish to change the order in which the modules are displayed in the Hierarchy Browser. By default, PeakVHDL adds new modules to the bottom of the Hierarchy Browser list. The order in which modules appear in the Hierarchy Browser is not significant in terms of the order of compilation, but you may want to establish a consistent standard so that you can more easily navigate in and manage your projects. For example, you may wish to place modules that are test benches at the top of the Hierarchy Browser, and maintain lower-level modules in a lower position in the list.

To move an existing module to a new position in the list, simply select that module by clicking once with the mouse, then select either **Move Module Up** or **Move Module Down** from the **File** menu.

#### Summary

This chapter has provided a quick introduction to the design management features of PeakVHDL. Subsequent chapters will show how you can quickly create new VHDL source modules using the Wizard features, and how you can simulate and debug your PeakVHDL projects.

# **Chapter 4: Using the VHDL Wizard**

The VHDL Wizard is a PeakVHDL feature that allows you to quickly and easily create new VHDL modules and test benches. The VHDL Wizard prompts you to enter a list of ports (input and output signals) describing the interface to your new design module, and from that list of ports automatically generates a template module or test bench.

After the template module or test bench has been created, you can modify it to add the desired functionality and/or test stimulus.

Chapter 4 is a step-by-step tutorial designed to show you how the PeakVHDL Wizards can make the creation of new design modules fast and easy.

Before beginning this tutorial, you should create a new, empty project as described in Chapter 3.

## Invoking the New Module Wizard

To create a new VHDL module using the VHDL Wizard:

- **1.** Select the New Module from the File menu, or click on the New Module icon.

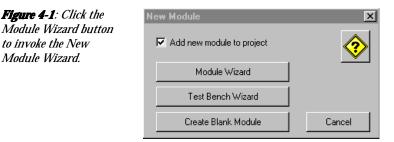

- **2.** When the New Module dialog appears, click on the Module Wizard button as shown in Figure 4-1.

# Specifying the Port List

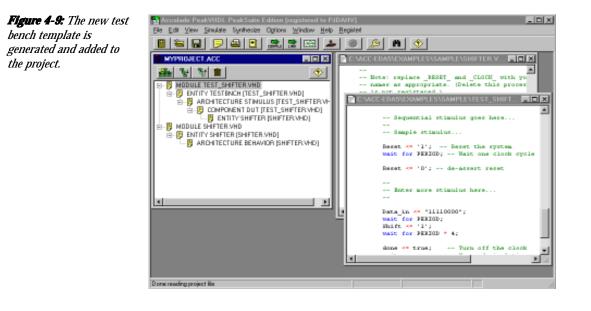

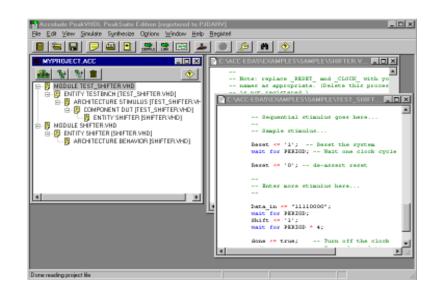

Figure 4-1: Click the

to invoke the New Module Wizard.

> The Module Wizard generates a template VHDL source file based on the I/O specification (the *port list*) that you provide. Entering your I/O is easy: just enter the port names, one at a time, along with their direction (or *mode*, in VHDL jargon) and type. The Module Wizard helps you by providing commonlyused modes and types in drop-down selection lists, and by checking to make sure the names that you enter are valid VHDL identifiers.

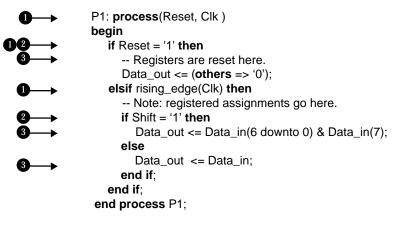

> For this tutorial example, we will create a simple shift register that accepts 8-bit data, and shifts (rotates) this data one bit position on the next rising edge of the clock. To describe the top-level entity and interface to this sample design in the Module Wizard:

- **1.** Enter the name of the new module (its VHDL entity name) in the Entity Name field.

- **2.** Enter the name of the new module's architecture in the Architecture Name field, or simply leave the field with its default value (architecture name **behavior**).

Figure 4-2: Use the Module Wizard to quickly describe the interface to your new module. Each port of the module is entered with a name, direction and type. You can edit the port list at any time before clicking the Create button.